# **MORNSUN®**

# TD551S422HW SOIC20 package isolated RS485 Full Duplex Transceiver

#### **Features**

- Ultra-small, ultra-thin, chip scale SOIC20 package

- Compliant with TIA/EIA-485-A standard

- Power supply 5.0V

- Integrated efficient isolation power supply with overload and short circuit protection

- I/O power supply range supports 5V microprocessors

- High isolation to 4000Vrms

- Bus-Pin ESD protection up to 15kV(HBM)/±4kV(Contact discharge)

- · Baud rate up to 20Mbps

- High common mode transient immunity 180kV/µs (typical value)

- Nanosecond level communication delay

- 1/8 unit load—up to 256 nodes on a bus

- Bus fail-safe

- Bus driver short circuit protection

#### **Applications**

- Industrial Automation

- Building Automation

- Smart Electricity Meter

- Remote Signal Interaction, Transmission

# Package

#### **Functional Description**

TD551S422HW is a full-duplex enhanced transceiver designed for RS-485/RS-422 data bus networks, has high electromagnetic immunity and low radiation characteristics which is fully compliant with TIA/EIA-485-A standard and is suitable for data transmission of up to 20Mbps. Receivers have an exceptionally high input impedance, which places only 1/8 of the standard load on a shared bus and up to 256 transceivers.

The TD551S422HW device has high insulation capacity, which helps to prevent noise and surges on the data bus or other circuits from entering the local grounding terminal, thereby interfering or damaging sensitive circuits. High CMTI capability can ensure the correct transmission of digital signals. On the basis of traditional IC, the focus is on strengthening the reliability design of A, B, Y and Z pins, including driver overcurrent protection and enhanced ESD design. The A, B, Y and Z ports can withstand ESD up to ±15kV (HBM) and ±4kV (contact discharge).

#### **Contents**

| 1 | Hom   | e                                  |   |

|---|-------|------------------------------------|---|

|   | 1.1   | Feature and Package                | 1 |

|   | 1.2   | Applications                       | 1 |

|   | 1.3   | Functional Description             | 1 |

| 2 | Pin F | Package and internal block diagram | 2 |

| 3 | IC R  | elated Parameters                  | 3 |

|   | 3.1   | Absolute Maximum Rating            | 3 |

|   | 3.2   | Recommended Operating Conditions   | 3 |

|   | 3.3   | Electrical Characteristics         | 4 |

|   | 3.4   | Transmission Characteristics       | 5 |

|   | 3.5   | Physical Characteristics           | 6 |

| 4  | Parameter testing circuit    | 6  |

|----|------------------------------|----|

| 5  | Detailed Description         | 7  |

| 6  | Application Circuit          | 7  |

| 7  | Suggestions for Power Supply | 8  |

| 8  | Order Information            | 9  |

| 9  | Package Information          | 10 |

| 10 | Tape & Reel Information      | 11 |

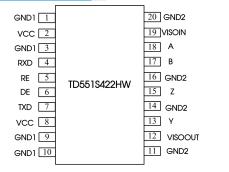

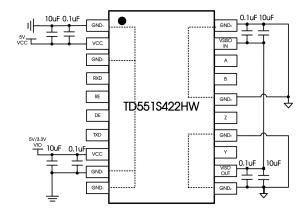

### Pin Connection

Note: All GND<sub>1</sub> Pin are internally connected;

Pin11&14 and Pin16&20 GND<sub>2</sub> are not internally connected.

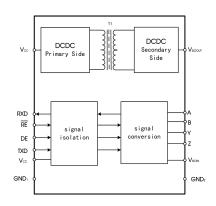

### Internal Block

# Function Table

| Letter | Description    |

|--------|----------------|

| Н      | High-Level     |

| L      | Low-Level      |

| X      | Unrelated      |

| Z      | High Impedance |

Table 1. Driver Function table

| <br>10000 11 20000 10000 |        |      |   |  |  |

|--------------------------|--------|------|---|--|--|

| TVD                      | DE     | Outp |   |  |  |

| TXD                      | TXD DE | Y    | Z |  |  |

| Н                        | Н      | Н    | L |  |  |

| L                        | Н      | L    | Н |  |  |

| X                        | L      | Z    | Z |  |  |

Table 2. Receiver Function table

| Table 2. 1 (cool of 1 affection table   |    |             |  |  |  |

|-----------------------------------------|----|-------------|--|--|--|

| Difference input $V_{ID} = (V_A - V_B)$ | RE | RXD         |  |  |  |

| -0.02 V ≤ ViD                           | L  | Н           |  |  |  |

| -0.22 V < VID < -0.02V                  | L  | Uncertainty |  |  |  |

| V <sub>ID</sub> ≤ -0.22 V               | L  | L           |  |  |  |

| Х                                       | Н  | Z           |  |  |  |

| Open circuit                            | L  | Н           |  |  |  |

Note:

- ① When driving status, the DE and  $\overline{\text{RE}}$  pins are connected to a high level;

- ② When receiving status, the DE and  $\overline{RE}$  pins are connected to a low level;

### Pin Descriptions

| Pin Number | Pin Name         | Pin Functions                                                                                                                                                         |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND₁             | Logic side reference ground.                                                                                                                                          |

| 2          | V <sub>cc</sub>  | Power supply. By using 0.1uF and 10uF ceramic capacitance ground (GND <sub>1</sub> ).                                                                                 |

| 3          | GND₁             | Logic side reference ground.                                                                                                                                          |

| 4          | RXD              | Receiver Output Data.                                                                                                                                                 |

| 5          | RE               | Receiver enable input. When $\overline{RE}$ is low, if $(A - B) \ge -20$ mV, then RXD = high. if $(A - B) \le -220$ mV, then RXD = low.                               |

| 6          | DE               | Driver enable input. When DE is high, outputs are enabled. When DE is low, outputs are high impedance.  Drive DE low and $\overline{RE}$ high to enter shutdown mode. |

| 7          | TXD              | Driver Input.                                                                                                                                                         |

| 8          | Vcc              | Power supply. By using 0.1uF and 10uF ceramic capacitance ground (GND <sub>1</sub> ).                                                                                 |

| 9          | GND₁             | Logic side reference ground.                                                                                                                                          |

| 10         | GND₁             | Logic side reference ground.                                                                                                                                          |

| 11         | GND <sub>2</sub> | Bus side reference ground.                                                                                                                                            |

| 12         | Visoout          | Isolate the power supply VISO output pin. Close to this pin, 0.1uF and 10uF ceramic capacitors must be connected to the bus side reference ground (GND2).             |

| 13         | Y                | RS422 Bus Y wire pin.                                                                                                                                                 |

| 14         | GND <sub>2</sub> | Bus side reference ground.                                                                                                                                            |

| 15         | Z                | RS422 Bus Z wire pin.                                                                                                                                                 |

| 16         | GND <sub>2</sub> | Bus side reference ground. The pin needs to be connected to pin14 in application.                                                                                     |

| 17         | В                | RS422 Bus B wire pin.                                                                                                                                                 |

| 18         | Α                | RS422 Bus A wire pin.                                                                                                                                                 |

| 19         | Visoin           | Isolate the power output. Close to this pin, 0.1uF and 10uF ceramic capacitors must be connected to the bus side reference ground (GND2).                             |

| 20         | GND₂             | Bus side reference ground. The pin needs to be connected to pin14 in application.                                                                                     |

# **Absolute Maximum Ratings**

General test conditions: Free-air, normal operating temperature range (Unless otherwise specified).

| Parameters                          | Unit                           |

|-------------------------------------|--------------------------------|

| Supply voltage, Vcc                 | -0.5V to +6V                   |

| Output voltage, Vin                 | -0.5V to V <sub>CC</sub> +0.5V |

| Output current Io                   | -10mA to +10mA                 |

| Junction temperature T <sub>J</sub> | <150°C                         |

| Operating temperature range         | -40°C to +125°C                |

| Storage temperature range           | −65°C to +150°C                |

Important: Exposure to absolute maximum rated conditions for an extended period may severely affect the device reliability, and stress levels exceeding the "Absolute Maximum Ratings" may result in permanent damage.

# **Recommended Operating Conditions**

| Symbol                                   | Recommended Operating Condition       | Min. | Тур. | Max. | Unit       |

|------------------------------------------|---------------------------------------|------|------|------|------------|

| Vcc                                      | Supply voltage                        | 4.5  | 5.0  | 5.5  |            |

| Vı                                       | A, B, Y, Z pin voltage                | -7   |      | 12   |            |

| V <sub>ID</sub>                          | A, B, Y, Z differential input voltage | -12  |      | 12   | V          |

| V <sub>IH</sub> High-level input voltage |                                       | 2    |      |      |            |

| V <sub>IL</sub>                          | Low-level input voltage               |      |      | 0.8  |            |

| T <sub>A</sub>                           | Operating temperature range           | -40  | 25   | 125  | $^{\circ}$ |

| DR                                       | Signaling rate                        |      |      | 20   | Mbps       |

# Electrical Characteristics

| Symbol                 | Parameter                                                 | Conditions                                         | Min.          | Тур.          | Max. | Unit  |

|------------------------|-----------------------------------------------------------|----------------------------------------------------|---------------|---------------|------|-------|

| Driver                 |                                                           |                                                    |               |               |      | ,     |

| N/ 1                   | Comment would be the state of the state of                | No load                                            | 4.5           |               | 5.2  |       |

| V <sub>OD</sub>        | Common mode output voltage                                | RL=60 Ω                                            | 1             |               | 3    | V     |

| 17.7                   | Absolute value of differential output                     | No load                                            | 4.5           |               | 5.43 | V     |

| V <sub>OD3</sub>       | voltage                                                   | RL=60 Ω                                            | 1.5           |               | 3    | V     |

| $\Delta V_{\text{OD}}$ | Δ V <sub>OD</sub>   for complementary output states       | No load , Figure 11                                | -0.2          |               | 0.2  | V     |

| $V_{IH}$               | High level output voltage                                 | TXD, DE, RE                                        | 2             | 5             | 5.5  | V     |

| V <sub>IL</sub>        | Low level output voltage                                  | TXD, DE, RE                                        | 0             |               | 0.8  | V     |

| I <sub>A</sub>         | - Driver short-circuit current                            |                                                    |               | ±100          | ±200 | m A   |

| I <sub>B</sub>         | - Driver short-circuit current                            |                                                    |               | ±100          | ±200 | mA mA |

| CMTI                   | Common mode transient immunity                            | V <sub>CM</sub> = 1200V; Figure 16                 |               | 180           | -    | kV/μs |

| Receiver               |                                                           |                                                    |               |               |      |       |

| VIT(+)                 | Positive differential input threshold voltage             | -7 V ≤ V <sub>CM</sub> ≤ +12 V                     |               | -             | -20  | mV    |

| VIT(-)                 | Negative differential input threshold voltage             | -7 V ≤ V <sub>CM</sub> ≤ +12 V                     | -220          |               |      | mV    |

| V <sub>hys</sub>       | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> ) | -7 V ≤ V <sub>CM</sub> ≤ +12 V                     |               | 30            |      | mV    |

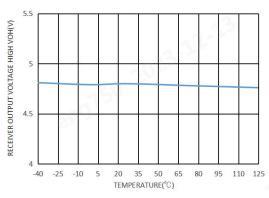

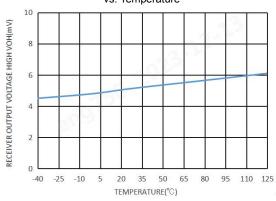

| Vон                    | RXD high level output voltage                             |                                                    | Vcc - 0.4     | 4.8           |      | V     |

| Vol                    | RXD low level output voltage                              |                                                    | 0             | 0.2           | 0.4  | V     |

| l <sub>A</sub>         | Receiver output current                                   |                                                    |               | ±100          | ±200 | A     |

| I <sub>B</sub>         | Receiver output current                                   |                                                    |               | ±100          | ±200 | mA mA |

| I <sub>IH</sub>        | Input high-level leakage current RE                       | V <sub>IH</sub> =2V                                |               |               | 20   |       |

| I <sub>IL</sub>        | Input low-level leakage current RE                        | V <sub>IH</sub> =0.8V                              | -20           |               |      | uA    |

| Rid                    | Differential input resistance(A, B)                       | -7 V ≤ V <sub>CM</sub> ≤ +12 V                     | 96            |               |      | kΩ    |

| Power supply           | and safeguard characteristic                              |                                                    |               |               |      |       |

| V <sub>ISO</sub>       | Isolated power output voltage                             | VCC=5V, distribution unloaded, signal fully loaded | 4.80          | 5.06          | 5.30 | V     |

|                        | Conducted Disturbance                                     | CISPR                                              | 32/EN55032 CL | ASS B; Figure | 22   |       |

| EMI                    | Radiated Disturbance                                      | CISPR32/EN55032 CLASS A; Figure 22                 |               |               | 22   |       |

| =0-                    | HBM Mode                                                  | Z, Y, A, B ports                                   |               |               | ±15  | kV    |

| ESD                    | Contact discharge mode                                    | Z, Y, A, B ports                                   |               |               | ±4   | kV    |

|                        | -                                                         | Leakage current <1mA                               |               |               | 6000 | VDC   |

|                        |                                                           | Rise time 3s, fall time 1s,<br>Test time 1s        |               |               | 4000 | VAC   |

| $V_{IO}$               | Insulate voltage                                          | Leakage current <1mA                               |               |               | 5000 | VDC   |

|                        |                                                           | Rise time 3s, fall time 1s,<br>Test time 60s       |               |               | 3500 | VAC   |

| Rio                    | Insulate impedance                                        | 1000 000                                           | 1             |               |      | GΩ    |

# **Transmission Characteristics**

| Symbol                              | Parameter                                              | Conditions                                                           | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| -                                   | Data rate                                              | Duty 40% ~ 60%                                                       |      |      | 20   | Mbps |

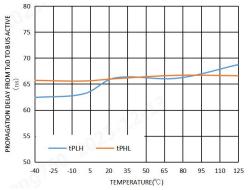

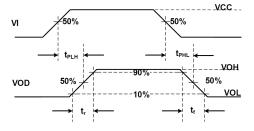

| T <sub>PHL</sub> ,T <sub>PLH</sub>  | Driver propagation delay                               |                                                                      |      | 50   | 90   | ns   |

| T <sub>PHL</sub> -T <sub>PLH</sub>  | Driver skew (  T <sub>PHL</sub> - T <sub>PLH</sub>   ) | $R_L$ =60 $\Omega$<br>$C_{L1}$ = $C_{L2}$ =50pF<br>Figure12 Figure15 |      |      | 25   | ns   |

| $T_R,T_F$                           | Driver rise/fall time                                  |                                                                      |      | 6    | 25   | ns   |

| t <sub>PZH</sub> / t <sub>PZL</sub> | Drive off enable propagation delay                     |                                                                      |      |      | 80   | ns   |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | Drive Enable Propagation Delay                         |                                                                      |      | 50   | 80   | ns   |

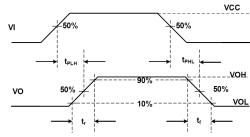

| T <sub>PHL</sub> ,T <sub>PLH</sub> | Receiver propagation delay                                                 | R <sub>L</sub> =60Ω                    | <br>70 | 110 | ns |

|------------------------------------|----------------------------------------------------------------------------|----------------------------------------|--------|-----|----|

| T <sub>PHL</sub> -T <sub>PLH</sub> | Receiver propagation delay                                                 | C <sub>L</sub> = 15pF , Figure13       | <br>   | 25  | ns |

| $T_R,T_F$                          | Receiver rise/fall time                                                    |                                        | <br>2  | 10  | ns |

| t <sub>PLH</sub>                   | Receive off enable propagation delay, Output low-level to high-level time  | $R_L=60\Omega$<br>$C_{L1}=C_{L2}=50pF$ | <br>   | 80  | ns |

| t <sub>PHL</sub>                   | Receive enable propagation delay time, Output high-level to low-level time | Figure13 Figure14                      | <br>   | 80  | ns |

# **Physical Specifications**

| Parameters | Value     | Unit |

|------------|-----------|------|

| Weight     | 0.6(Typ.) | g    |

# Typical Performance Curves

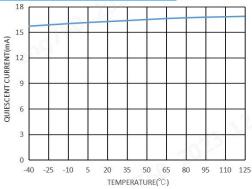

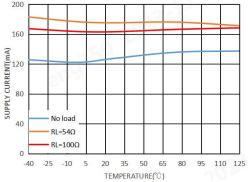

Figure 1. Quiescent Current vs. Temperature

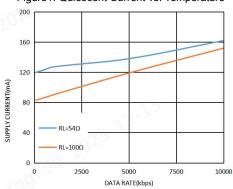

Figure 3. Supply Current vs. Data Rate

Figure 5. Receiver Output High Voltage vs. Temperature

Figure 2. Supply Current vs. Temperature

5

1.25

RL=540

RL=1000

-40 -25 -10 5 20 35 50 65 80 95 110 125

Figure 4. BUS Output Differential Voltage vs. Temperature

Figure 6. Receiver Output Low Voltage vs. Temperature

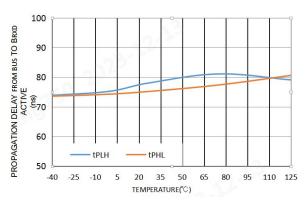

Figure 7. Propagation Delay from TXD to Bus Active vs. Temperature

Figure 8. Propagation Delay from BUS to RXD Active vs. Temperature

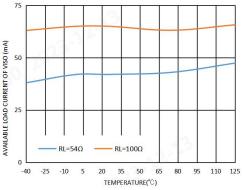

Figure 9. Available Load Current Of VISO vs. Temperature

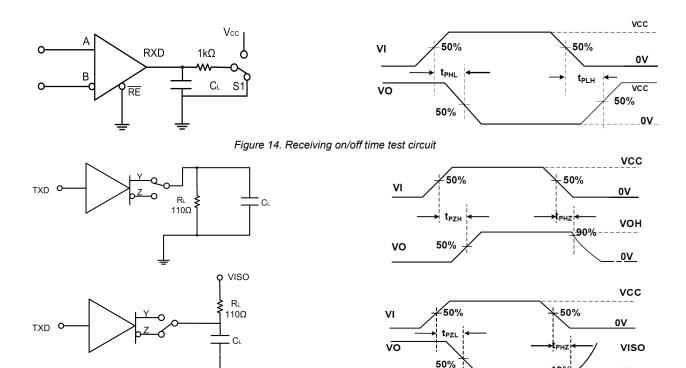

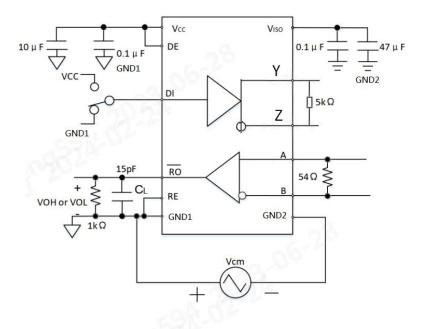

# Parameter testing circuit

Note: Test condition load capacitance includes test probe and fixture parasitic capacitance (no special instructions). The rising and falling edges of the test < 6ns. frequency 100kHz. duty50%. resistance  $Z_0$  = 54 $\Omega$ .

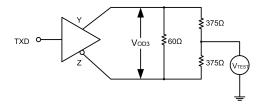

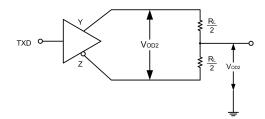

Figure 10.Common mode output test circuit

Note: CL includes parasitic capacitance of fixtures and instruments

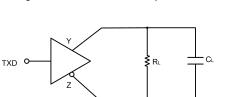

Figure 11. Differential output test circuit

Figure 12. Drive propagation delay test circuit and wave forms

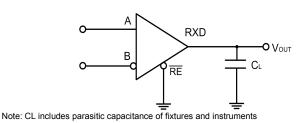

Figure 13. Receiver propagation delay test circuit and wave forms

Note: CL includes parasitic capacitance of fixtures and instruments

Figure 15. Driver On/Off Time Test Circuit

Figure 16. CMTI Test Circuit

#### **Detailed Description**

TD551S422HW is a full-duplex enhanced RS-485/RS-422 isolated transceiver with isolated power supply. In addition to an isolated power supply, each transceiver contains a drive and a receiver. The transceiver has a standby bus failure protection function to ensure that the receiver output is high when the receiver input is open, short, or when the bus is idle.equipped with failure safety, overcurrent protection, and overheating protection functions.

Bus failure protection: When the receiver input is short circuited or open, and all drivers hanging on the terminal matching transmission line are disabled (idle), the TD551S422HW product can ensure that the receiver output logic is high. This is achieved by setting the input threshold of the receiver to -220mV and -20mV, respectively. If the input voltage (A-B) of the differential receiver is ≥ -20mV, RO is the logic high level; If the voltage (A-B) is ≤ -220mV, RO is the logic low level. When all transmitters connected to the terminal matching bus are disabled, the differential input voltage of the

.0V\_

receiver will be pulled to 0V through the terminal resistor. Based on the receiver threshold, a logic high level with a minimum noise tolerance of -20mV can be achieved. The threshold voltage from 220mV to -20mV is in accordance with EIA/TIA-485 standards.

The bus load capacity (256 point): standard RS485 receiver input impedance is defined as  $12k\Omega$  (unit load). A standard RS485 driver can drive at least 32 load units. TD551S422HW bus receiver designed by 1/8 unit load, the input impedance is greater than  $96k\Omega$ . As a result, the bus allows access to more transceivers (up to 256). TD551S422HW can also be mixed with the standard RS485 transceiver with 32 unit loads (cumulative receiver load cannot exceed 32 units).

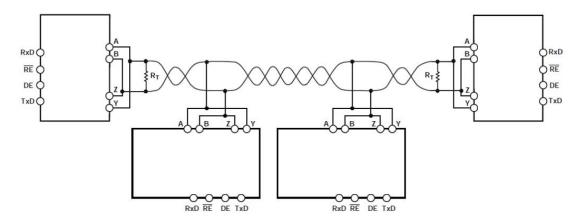

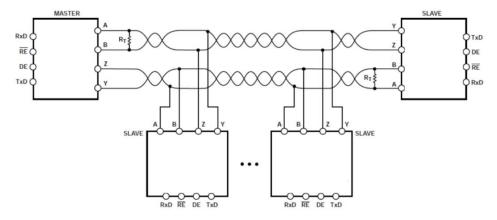

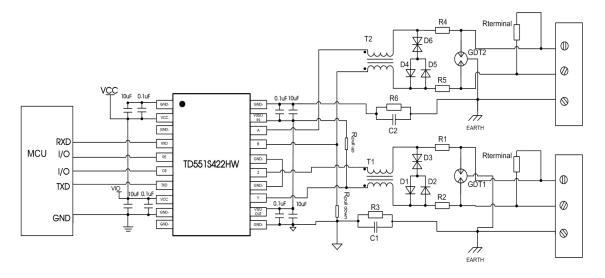

#### **Application Circuit**

Figure 18. Typical Application Circuit (Half-Duplex Network Topology)

Figure 19. Typical application circuit (full-Duplex Network Topology)

Figure 20. Typical Application Diagram

Figure 21. Port protection circuit for harsh environments

#### Parameter Description:

| Component  | Recommended part, value | Component             | Recommended part, value |  |  |

|------------|-------------------------|-----------------------|-------------------------|--|--|

| R3, R6     | 1ΜΩ                     | R1, R2, R4, R5        | 2.7Ω/2W                 |  |  |

| C1, C2     | 1nF, 2kV                | D1, D2, D4, D5        | 1N4007                  |  |  |

| T1, T2     | ACM2520-301-2P          | D3, D6                | SMBJ8.5CA               |  |  |

| GDT1, GDT2 | B3D090L                 | R <sub>terminal</sub> | 120Ω                    |  |  |

As the modules internal A / B / Z / Y lines come with its own ESD protection, which generally satisfy most application environments without the need for additional ESD protection devices. For harsh and noisy application environments such as motors, high voltage/current switches, lightning and similar however, we recommended that the user protects the module's A / B / Z / Y lines with additional measures and external components such as TVS tube, common mode inductors, Gas discharge tube, shielded twisted pair of wires with the same single network Earth point. Figure 21 shows our recommended circuit diagram for such type of applications with components and values given in the table above. This recommendation is for reference only and may have to be adapted accordingly with appropriate component values in order to match the actual situation and application.

- Note 1: Select the R<sub>terminal</sub> according to the actual application.

- Note 2: When using the port protection circuit, you need to slow down the baud rate.

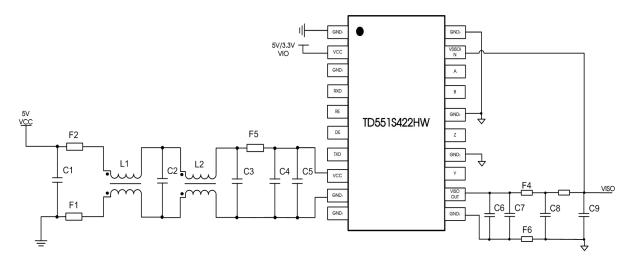

Figure 22. circuit for EMI

#### Parameter Description:

| Component                     | Recommended part, value            |  |  |  |  |

|-------------------------------|------------------------------------|--|--|--|--|

| F1, F2, F3, F4, F5, F6,<br>F7 | UP1608U601-1R3TF<br>(DCR 0.15ΩMax) |  |  |  |  |

| C1, C2, C3, C4, C7,<br>C8, C9 | 10uF                               |  |  |  |  |

| C5, C6                        | 0.1uF                              |  |  |  |  |

| L1                            | Nickel core: 138uH                 |  |  |  |  |

| L2                            | Nickel core: 78uH                  |  |  |  |  |

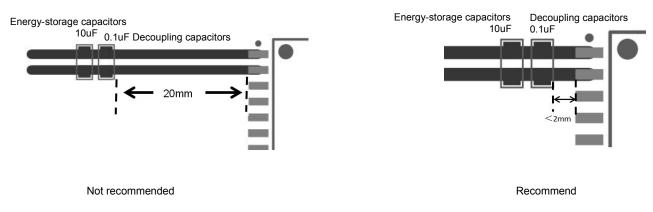

#### PCB design description:

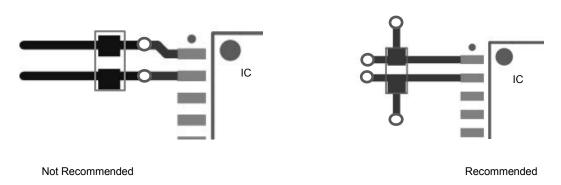

1. The decoupling capacitors and energy storage capacitors of VCC and GND1, VISO and GND2 should be placed as close to the chip pins as possible to reduce the loop area and parasitic inductance of PCB wiring. Generally, it should be controlled within 2mm. The decoupling capacitor is placed near the chip, and the energy storage capacitor is placed on the outside. As shown in Figure 23-1.

Figure 23-1

- 2. When wiring, the power line width should be designed to be at least 0.5mm.

- 3. When it is necessary to place vias in the power supply line and ground wire, the position of the vias should be on the outer side of the capacitor relative to the chip pins, rather than between the capacitor and the chip, as shown in Figure 23-2 to reduce the impact of parasitic inductance in the vias.

Figure 23-2

#### Recommendations

- ① The product does not support hot-plugging.

- ② TXD external inputs should have pull-up resistors added as appropriate if drive capability is insufficient.

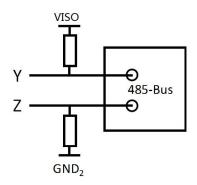

- 3 In order to maintain the bus idle stability, it is necessary to pull up Y to VISO and pull down Z to GND2 in at least one node at the bus end, while the pull-up and down resistors of the overall network have a parallel value of  $380\Omega \sim 420\Omega$  (0.2W).

Figure 24. Typical Pull-Up and Pull-Down Resistor Connections

4 High when the product's internal DE and TXD are overhanging, and low when  $\overline{\text{RE}}$  is built-in overhanging.

# **Ordering Information**

| Part number | Package | Number of pins | Product marking | Tape & Reel |  |

|-------------|---------|----------------|-----------------|-------------|--|

| TD551S422HW | SOIC    | 20             | TD551S422HW     | 290/REEL    |  |

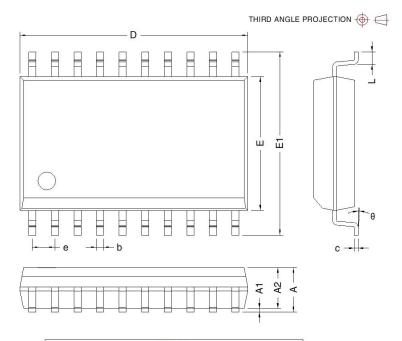

# Package Information

|        |        | SOIC-20 |                 |                                  |  |  |

|--------|--------|---------|-----------------|----------------------------------|--|--|

| Mark   | Dimens | ion(mm) | Dimension(inch) |                                  |  |  |

| IVIAIK | Min    | Max     | Min             | Max                              |  |  |

| Α      | _      | 2.65    | _               | 0.104                            |  |  |

| A1     | 0.10   | 0.30    | 0.004           | 0.012<br>0.093                   |  |  |

| A2     | 2.25   | 2.35    | 0.089           |                                  |  |  |

| D      | 12.70  | 12.90   | 0.500           | 0.508<br>0.299<br>0.413<br>0.040 |  |  |

| Е      | 7.40   | 7.60    | 0.291           |                                  |  |  |

| E1     | 10.10  | 10.50   | 0.398<br>0.028  |                                  |  |  |

| L      | 0.70   | 1.00    |                 |                                  |  |  |

| b      | 0.39   | 0.47    | 0.015           | 0.019                            |  |  |

| е      | 1.27(  | BSC)    | 0.05(BSC)       |                                  |  |  |

| c 0.25 |        | 0.29    | 0.010           | 0.011                            |  |  |

| θ      | 0°     | 8°      | 0°              | 8°                               |  |  |

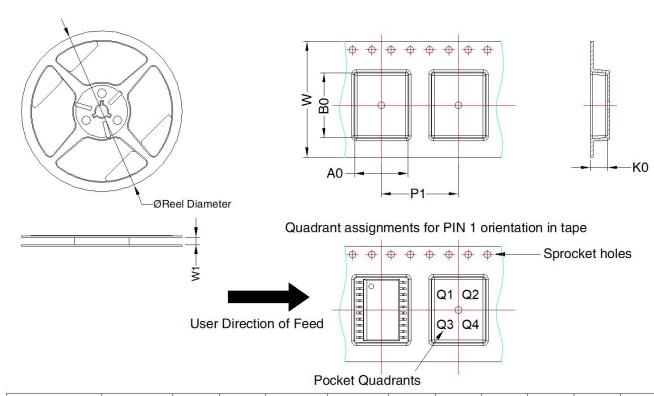

| Device      | Package<br>Type | Pin | MPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|-----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TD551S422HW | SOIC-20         | 20  | 290 | 178                      | 25.5                     | 11.1       | 13.5       | 3.5        | 16.0       | 24.0      | Q1               |

# MORNSUN Guangzhou Science & Technology Co., Ltd.

Address: No. 5, Kehui St. 1, Kehui Development Center, Science Ave., Guangzhou Science City, Huangpu District, Guangzhou, P. R. China Tel: 86-20-38601850 Fax: 86-20-38601272 E-mail: <a href="mailto:info@mornsun.cn">info@mornsun.cn</a> www.mornsun-power.com